# **VHDL & OPTICAL FIBER LAB**

# L AB MANUAL

# **VIII SEMESTER**

Department Of Electronics & Communication Engg Bhagwant university, Sikar road Ajmer

# LIST OF EXPERIMENTS

#### PART-I

Design of following ckt using appropriate software like VHDL/ FPGA.

- 1. 3-input NAND gate.

- 2. Half adder.

- 3. D-Latch.

- 4. Serial in-serial out shift register.

#### PART-II

To perform following experiments based on Fiber Optic Trainer.

- 1. To set up Fiber Optic Analog link.

- 2. To set up fiber Optic Digital link.

- 3. Measurement of Propagation loss and numerical aperture.

- 4. Characterization of laser diode and light emitting diode

#### PART-II

Schematic design and make Device Level Layout of following circuits.

- 1. BJT/FET Amplifier in various configuration..

- 2. Counters, Shift Registers & Sequence Decoders.

- 3. Various circuits with Op-Amp.

# PART- I

## **Object 1**:

Design of NAND Gate using appropriate software like VHDL/ FPGA.

#### <u>VHDL code</u> :

library IEEE;

```

use IEEE.STD_LOGIC_1164.ALL;

```

entity NAND\_GATE is

Port (A: in STD\_LOGIC;

Y: out STD\_LOGIC);

end NAND\_GATE;

architecture Behavioral of NAND\_GATE is

begin

PROCESS(A)

BEGIN

```

if(a='0' and b='0') then z <= '1';

```

```

if(a='0' and b='1') then z <= '1';

```

```

if(a='1' and b='0') then z <= '1';

```

```

if(a='1' and b='1') then z <= '0';

```

end if;

end process;

end Behavioral;

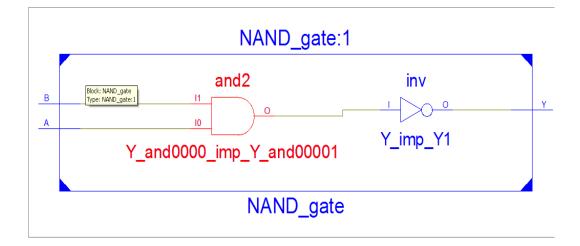

#### **RTL SCHEMATIC** :

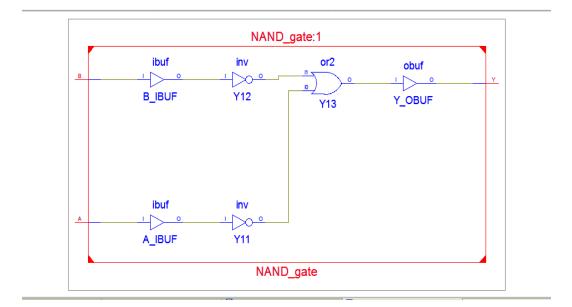

#### **TECHNOLOGY SCHEMATIC :**

#### WAVEFORM:

|       |       |      |              |              |        | 3,340,000 ps |              |               |              |               |

|-------|-------|------|--------------|--------------|--------|--------------|--------------|---------------|--------------|---------------|

| Name  | Yalue | 0 ps | 1,000,000 ps | 2,000,000 ps | 3,000, | 000 ps       | 4,000,000 ps | 15,000,000 ps | 6,000,000 ps | 17,000,000 ps |

| Ца а  | 1     |      |              |              |        |              |              |               |              |               |

| The y | 0     |      |              |              |        |              |              |               |              |               |

|       |       |      |              |              |        |              |              |               |              |               |

|       |       |      |              |              |        |              |              |               |              |               |

|       |       |      |              |              |        |              |              |               |              |               |

|       |       |      |              |              |        |              |              |               |              |               |

|       |       |      |              |              |        |              |              |               |              |               |

|       |       |      |              |              |        |              |              |               |              |               |

|       |       |      |              |              |        |              |              |               |              |               |

|       |       |      |              |              |        |              |              |               |              |               |

|       |       |      |              |              |        |              |              |               |              |               |

|       |       |      |              |              |        |              |              |               |              |               |

|       |       |      |              |              |        |              |              |               |              |               |

|       |       |      |              |              |        |              |              |               |              |               |

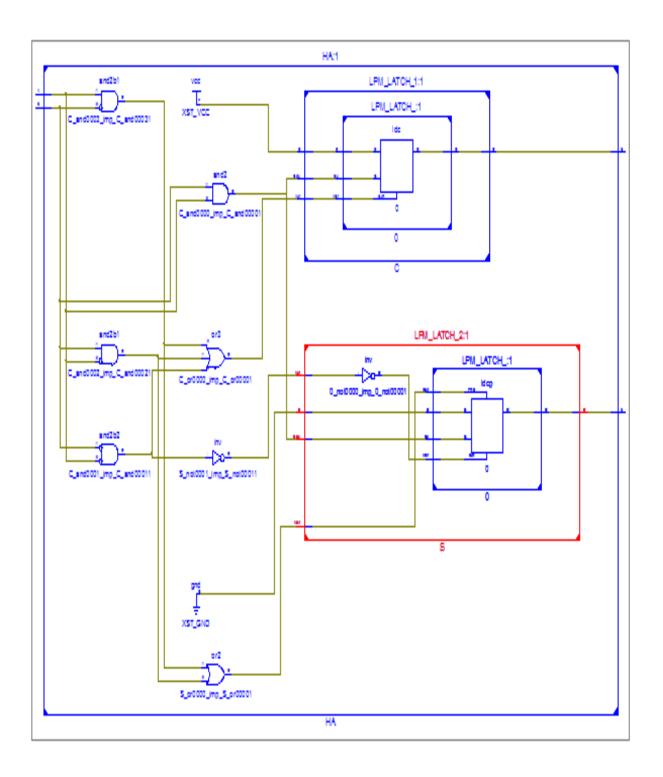

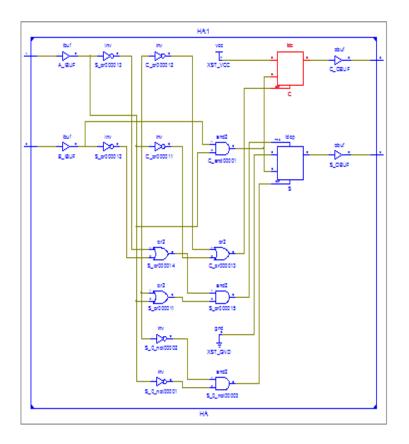

# **Object 2:**

Design of Half Adder using appropriate software like VHDL/ FPGA.

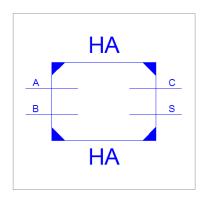

#### **BLOCK DIAGRAM:**

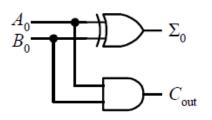

#### LOGIC DIAGRAM:

# Half-adder

#### TRUTH TABLE:

| Α | В | S | С |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

#### VHDL code :

Library ieee;

Use ieee.std\_logic\_1164.all;

entity FA is

Port ( a : in STD\_LOGIC;

b : in STD\_LOGIC;

s : in STD\_LOGIC;

cout : out STD\_LOGIC);

end FA;

architecture Behavioral of FA is

begin

process(a,b,cin)

begin

if(a='0' and b='0')then

s<='0';

c<='0';

elsif(a='0' and b='1')then

s<='1';

c<='0';

elsif(a='1' and b='0' )then

s<='1';

c<='0';

elsif(a='1' and b='1')then

s<='0';

c<='1';

end if;

end process;

end Behavioral;

#### **RTL SCHEMATIC**:

#### TECHNOLOGY SCHEMATIC:

#### WAVEFORM:

|                    |       |                  |              |              |              | 0,220,000 ps  |               |               |               |

|--------------------|-------|------------------|--------------|--------------|--------------|---------------|---------------|---------------|---------------|

|                    |       |                  |              |              |              |               |               |               |               |

| Name               | Value | 0 ps             | 2,000,000 ps | 4,000,000 ps | 6,000,000 ps | 18,000,000 ps | 10,000,000 ps | 12,000,000 ps | 14,000,000 ps |

| 1 <mark>1</mark> a | 1     |                  |              |              |              |               |               |               |               |

| Ц                  | 1     |                  |              |              |              |               |               |               |               |

| 🏰 s                | 0     |                  |              |              |              |               |               |               |               |

| 1 <mark>6</mark> c | 1     |                  |              |              |              |               |               |               |               |

|                    |       |                  |              |              |              |               |               |               |               |

|                    |       |                  |              |              |              |               |               |               |               |

|                    |       |                  |              |              |              |               |               |               |               |

|                    |       |                  |              |              |              |               |               |               |               |

|                    |       |                  |              |              |              |               |               |               |               |

|                    |       |                  |              |              |              |               |               |               |               |

|                    |       |                  |              |              |              |               |               |               |               |

|                    |       |                  |              |              |              |               |               |               |               |

|                    |       |                  |              |              |              |               |               |               |               |

|                    |       |                  |              |              |              |               |               |               |               |

|                    |       |                  |              |              |              |               |               |               |               |

|                    |       | V1 - 0.000.000   |              |              |              |               |               |               |               |

|                    |       | X1: 8,220,000 ps |              |              |              |               |               |               |               |

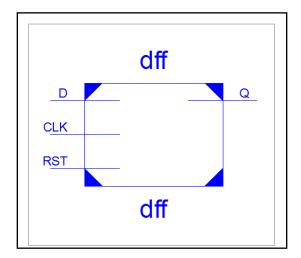

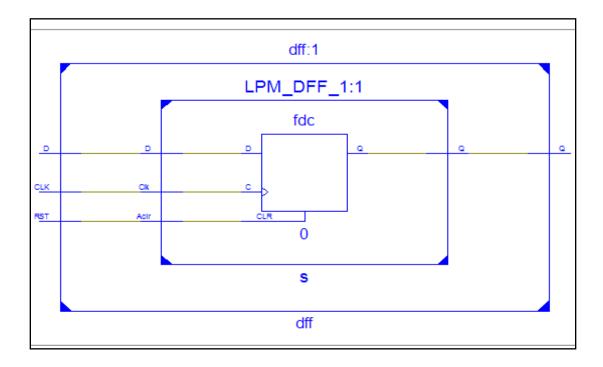

# **Object 3:**

Design of D flip flop using appropriate software like VHDL/ FPGA.

# **D- Flip flop**

## **Truth Table**

| D | Q |

|---|---|

| 0 | 0 |

| 1 | 1 |

#### VHDL code :

Library IEEE;

use IEEE.STD\_LOGIC\_1164.ALL;

entity dff is

Port ( D : in STD\_LOGIC;

CLK : in STD\_LOGIC;

RST : in STD\_LOGIC;

Q:out STD\_LOGIC);

end dff;

architecture Behavioral of dff is

signal s: std\_logic;

begin

process(D,CLK,RST)

begin

if(RST = '1')then

s <= '0';

elsif(CLK = '1' and CLK'event)then

s <= D;

end if;

end process;

Q <= s;

end Behavioral;

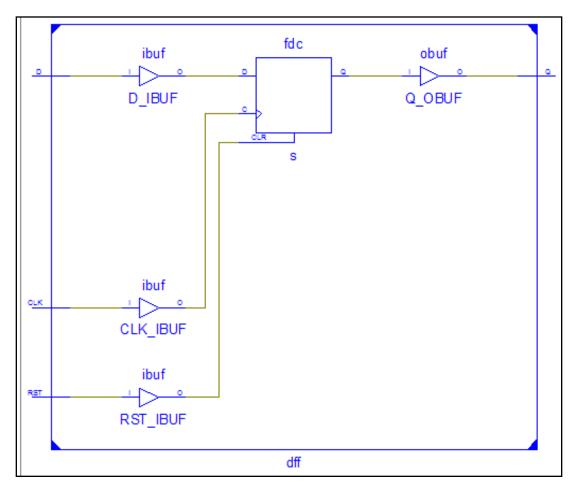

#### **RTL SCHEMATIC**:

## **TECHNOLOGY SCHEMATIC:**

## Waveform:

| Name                | Value | 0 ps | 20 ps | 140 ps | 60 ps 80 |

|---------------------|-------|------|-------|--------|----------|

| l <mark>la</mark> d | 1     |      |       |        |          |

| 🏪 clk               | 1     |      |       |        |          |

| 🏪 rst               | 0     |      |       |        |          |

| Ца а                | 1     |      |       |        |          |

| U <sub>lo</sub> s   | 1     |      |       |        |          |

|                     |       |      |       |        |          |

|                     |       |      |       |        |          |

## **Object 4**:

Design of Serial in-serial out shift register ckt using appropriate software like VHDL/ FPGA.

#### VHDL code :

```

entity siso_reg is

Port ( clk1 : in STD_LOGIC;

rst1 : in STD_LOGIC;

s_in : in STD_LOGIC;

s_out : out STD_LOGIC);

end siso_reg;

architecture Behavioral of siso reg is

component dff_en is

port (D,clk,clr :in std_logic;

Q: out std_logic);

end component;

signal s1,s2,s3 :std_logic;

begin

u1:dff_en

port map( D => s_in,

clk => clk1,

clr => rst1,

Q => s1);

u2:dff_en

port map( D => s1,

clk => clk1,

clr => rst1,

Q => s2);

u3:dff_en

port map( D => s2,

clk => clk1,

clr => rst1,

Q => s3);

u4:dff_en

port map( D => s3,

clk => clk1,

clr => rst1,

Q => s_out);

```

end Behavioral;

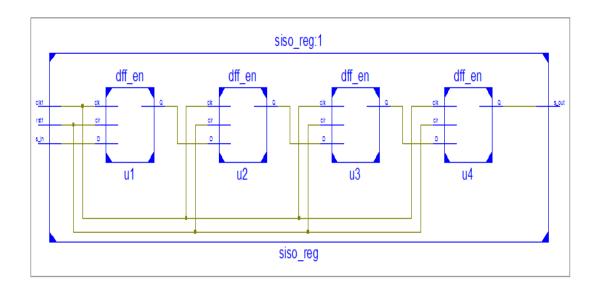

#### **RTL SCHEMATIC:**

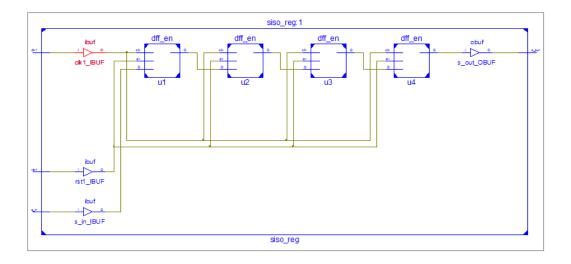

## TECHNOLOGY SCHEMATIC:

#### WAVEFORM:

|               |       |                  |              |              |              |              |              | <mark>4,</mark> | 000,234 ps   |

|---------------|-------|------------------|--------------|--------------|--------------|--------------|--------------|-----------------|--------------|

| ame           | Value | 3,999,900 ps     | 3,999,950 ps | 4,000,000 ps | 4,000,050 ps | 4,000,100 ps | 4,000,150 ps | 4,000,200 ps    | 4,000,250 ps |

| 🖫 clk1        | 0     |                  |              |              |              |              |              |                 |              |

| 堤 rst1        | 0     |                  |              |              |              |              |              |                 |              |

| lla s_in      | 1     |                  |              |              |              |              |              |                 |              |

| lla s_out     | 1     |                  |              |              |              |              |              |                 |              |

| Va s1         | 1     |                  |              |              |              |              |              |                 |              |

| <b>16</b> s2  | 1     |                  |              |              |              |              |              |                 |              |

| l <b>a</b> s3 | 1     |                  |              |              |              |              |              |                 |              |

|               |       | X1: 4,000,234 ps | <u> </u>     |              |              |              |              |                 |              |

## PART-II

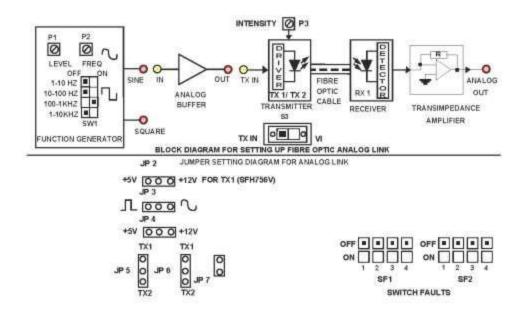

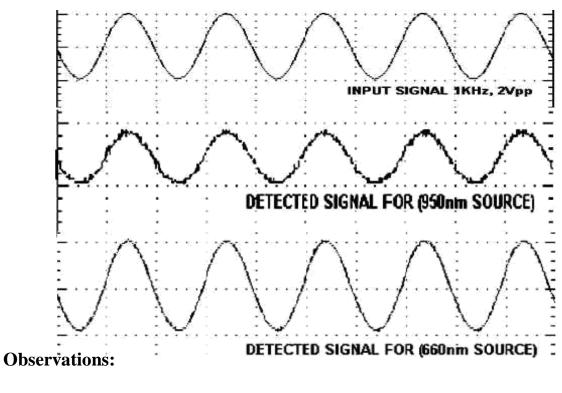

#### SETTING UP FIBER OPTIC ANALOG LINK

## **OBJECT 1:**

To establish fiber optic analog link and to study the relationship between the input signal & received signal.

## **Equipment required**

Link-A kit, 1 Meter Fiber cable, 20 MHz Dual Channel Oscilloscope, Power supply

#### THEORY

Fiber Optic Links can be used for transmission of digital as well as analog signals. Basically a fiber optic link contains three main elements, a transmitter, an optical fiber and a receiver. The transmitter module takes the input signal in electrical form and then transforms it into optical (light) energy containing the same information. The optical fiber is the medium, which carries this energy to the receiver. At the receiver, light is converted back into electrical form with the same pattern as originally fed to the transmitter.

#### TRANSMITTER

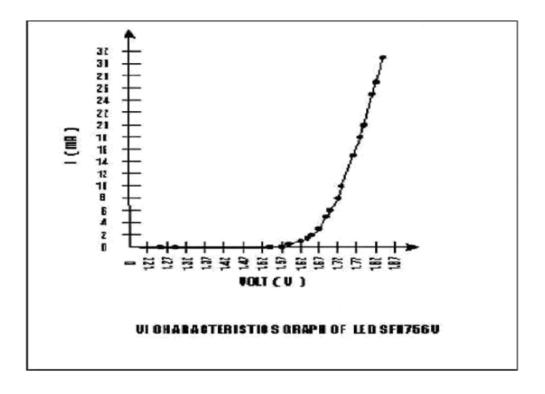

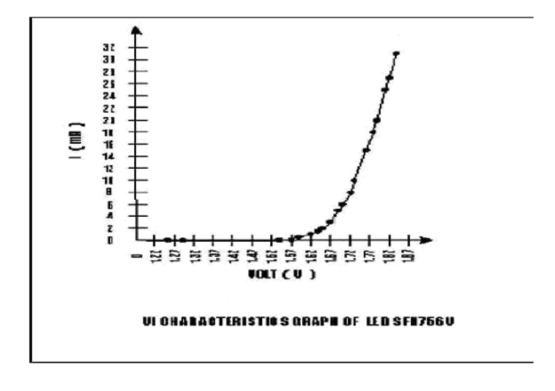

Fiber optic transmitters are typically composed of a buffer, driver and optical source. The buffer electronics provides both an electrical connection and isolation between the transmitter and the electrical system supplying the data. The driver electronics provides electrical power to the optical source in a fashion that duplicates the pattern of data being fed to the transmitter. Finally the optical source (LED) converts the electrical current to light energy with the same pattern. The LED SFH756V supplied with the kit operates inside the visible light spectrum. Its optical output is centered at near visible wavelength of 660 nm. The ED SFH450V supplied with the kit operates outside the visible light spectrum is broad, so a dark red glow can usually be seen when the LED is on. The LED SFH450V supplied with the kit operates outside the visible light spectrum. Its optical output is centered at near infrared wavelength of 950 nm.

#### RECEIVER

The function of the receiver is to convert the optical energy into electrical form, which is then conditioned to reproduce the transmitted electrical signal in its original form. The detector

SFH250V used in the kit has a diode type output. The parameters usually considered in the case of detector are it's responsivity at peak wavelength and response time. SFH250V has responsivity of about 4  $\mu$ A per 10  $\mu$ W of incident optical energy at 950 nm and it has rise and fall time of 0.01 $\mu$ sec. PIN photodiode is normally reverse biased. When optical signal falls on the diode, reverse current start to flow, thus diode acts as closed switch and in the absence of light intensity; it acts as an open switch. Since PIN diode usually has low responsivity, a trans impedance amplifier is used to convert this reverse current into voltage. This voltage is then amplified with the help of another amplifier circuit. This voltage is the duplication of the transmitted electrical signal.

#### Procedure

- 1. Slightly unscrew the cap of LED SFH 756V TX1 (660 nm) from kit. Do not remove the cap from the connector. Once the cap is loosened, insert the fiber into the cap and assure that the fiber is properly fixed. Now tight the cap by screwing it back. Keep INTENSITY pot P3 at minimum position i.e. fully anticlockwise.

- 2. Make the connections and jumper settings as shown in Fig. Connect the power supply cables with proper polarity to kit. While connecting this, ensure that the power supply is OFF.

- 3. Switch on the Power supply.

- 4. Select the frequency range of Function Generator with the help of Range Selection Switch SW1, frequency can be varied with pot P2. adjust the voltage LEVEL of the sine wave with pot P1 as per following setting FREQUENCY: 1 KHz, LEVEL: 2V p-p

- 5. Connect SINE post of the Function Generator section to IN post of Analog Buffer Section.

- 6. Connect OUT post of the Analog Buffer Section to TX IN post of TRANSMITTER.

- 7. Connect the other end of the fiber to detector SFH 250V (RX 1) in kit very carefully.

- 8. Check the output signal of the Analog Buffer at its OUT post in Kit. It should be same as that of the applied input signal.

- Observe the output signal from the detector at ANALOG OUT post on CRO by adjusting INTENSITY (Optical Power Control) Pot P3 in kit and you should get the reproduction of the original transmitted signal

- 10. To measure the analog bandwidth of the link, connect the external Signal Generator with 2Vp-p sine wave to IN post of Analog Buffer Section and vary the frequency of the input signal from 100 Hz onwards. Measure the amplitude of the received signal for each frequency reading.

- 11. Plot a graph of gain / Frequency. Measure the frequency range for which the response is flat.

Repeat the procedure 1 to 11 for IR LED 450V (950nm) TX2.

Frequency (Hz)

I/P Signal amplitude (Volts)

Output signal amplitude (Volts)

Gain = 20 log (V<sub>0</sub> / V<sub>i</sub> ) (dB)

## **Precautions:**

It is very important that the optical sources be properly aligned with the cable and the distance from the launched point and the cable be properly selected to ensure that the maximum amount of optical power is transferred to the cable.

## **Result:**

On optical fiber link is established. The frequency response is observed. A graph is drawn between gains in (dB) Vs frequency in Hz.

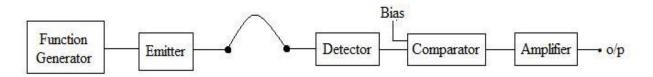

## SETTING UP FIBER OPTIC DIGITAL LINK

## **OBJECT 2:**

Study of a 650nm fiber optic digital link.

#### **Apparatus required:**

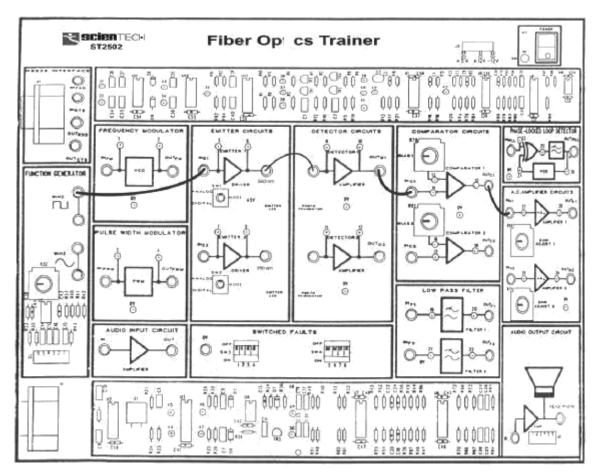

- 1. ST2502 trainer with power supply cords

- 2. Optical Fiber cable.

- 3. Cathode ray oscilloscope with necessary connecting probe.

#### **Theory:**

Fiber optic links can be used for transmission of digital as well as analog signals. Basically a fiber optic link contains three main elements : a transmitter, an optical fiber and a receiver. The transmitter module takes the input signal in electrical form and then transforms it into optical energy containing the same information. The optical fiber is the medium which takes the energy to the receiver. At the receiver, light is converted back into electrical form with the same pattern as fed to the transmitter.

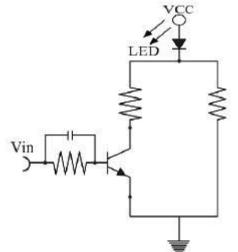

Transmitter:

Fiber optic transmitters are composed of a buffer, driver and optical source. The buffer provides both an electrical connection and isolation between the transmitter and the electrical system the data. The driver provides electrical power to the optical source. Finally, the optical source converts the electrical current to the light energy with the same pattern. The optical source used is LED. The simple driver circuit is shown below.

Fig.3.1 A simple drive circuit for binary digital transmission consisting a

common emitter saturating switch.

The transmitter section comprises of Function Generator which generates input signals that are going to be used as information to transmit through optical fiber.

The Fiber Optic Link:

Emitter and Detector circuit on board form the fiber optic link. This section provides the light source for the optic fiber and the light detector at the far end of the fiber optic links. The optic fiber plugs into the connectors provided in this part of the board. Two separate links are provided.

The Receiver:

The comparator circuit and AC amplifier circuit form receiver on the board.

## **Block Diagram:**

## **Procedure:**

- 1. Connect the power supply to the board.

- 2.Ensure that all switched faults are off.

- 3. Make the following connections.

- Connect the Function generator 1KHz square wave output to emitter"s input.

- Connect the Fiber optic cable between emitter output and detector"s input.

- Detector"s output to comparator"s input.

- Comparator"s output to AC amplifier"s input.

- 4. On the board, switch emitter"s driver to digital mode.

- 5. Switch ON the power.

6. Monitor both the inputs to comparator . Slowly adjust the comparator's bias preset, until DC level on the input lies midway between the high and low level of the signal on the positive input.

7. Observe the input to emitter with the output from AC amplifier and note that the two signals are same.

Fig.3.3 Connections on Trainer Kit

## **Observations:**

Input Voltage = 0.16V

Comparator output = 0.05V

Amplifier output = 1V

## **Result:**

The 650nm fiber optic Digital link has been established.

## MEASUREMENT OF PROPAGATION LOSS AND NUMERICAL APERTURE

#### **Object 3:**

To measurement of the Numerical Aperture (NA) of the fiber.

#### **Apparatus Required:**

- 1. ST2502 trainer with power supply cord

- 2. Optical Fiber cable.

- 3. Numerical Aperture measurement Jig/Paper & Scale.

To numerical aperture jig

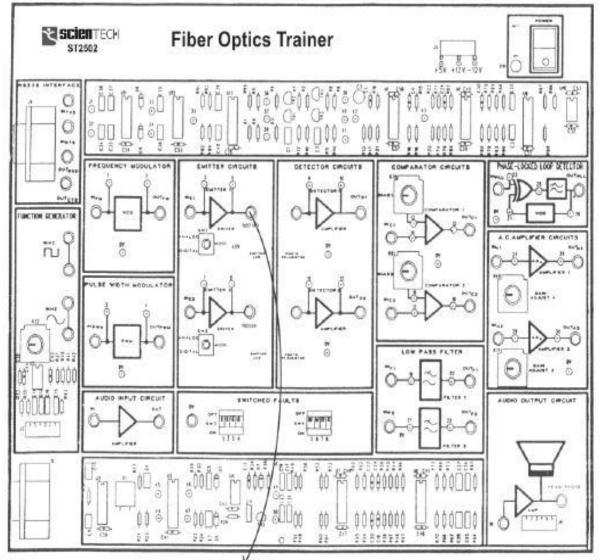

Fig.8.1 Connection diagram on ST502

#### **Theory:**

The numerical aperture refers to maximum angle at which the incident on fiber end is totally internally reflected and is transmitted along the fiber. The cone formed by rotation of this angle along the axis of the fiber is the cone of acceptance of fiber. if light ray should strike the fiber end within this cone of acceptance it will be transmitted properly else it is refracted out of fiber.

$$n\sin\theta_{\rm max} = \sqrt{n_{\rm core}^2 - n_{\rm clad}^2},$$

#### **Procedure:**

1. Connect the Power supply cord to mains supply and to the trainer ST2502.

2. Connect the frequency generator's 1 KHz sine wave output to input of emitter 1 circuit. Adjust its amplitude at 5Vpp.

3. Connect one end of fiber cable to the output socket of emitter 1 circuit and the other end to the numerical aperture measurement jig. Hold the white screen facing the fiber such that its cut face is perpendicular to the axis of the fiber.

4. Hold fiber vertically at a suitable distance to make the red spot .

5. Record the distance of screen from the fiber end L and note the diameter W of the spot.

Compute the numerical aperture from the formula given below-

$$NA=(W/2) / \sqrt{(W/2)^2 + L^2}$$

**Result** : The N.A. of fiber measured is 0.34 using trigonometric formula.

## CHARACTERIZATION OF LASER DIODE AND LIGHT EMITTING DIODE

## **Object 4:**

To study the VI characteristics of fiber optic LED'S. and Photo Detector

## **Equipment required**

Link-A kit, 20 MHz Dual Trace Oscilloscope, 1 & 3 Meter Fiber cable, Power supply, Voltmeter, Current meter, Jumper Connecting Wires-4.

## Theory

In optical fiber communication system, electrical signal is first converted into optical signal with the help of E/O conversion device as LED. After this optical signal is transmitted through optical fiber, it is retrieved in its original electrical form with the help O/E conversion device as photo detector.

Different technologies employed in chip fabrication lead to significant variation in parameters for the various emitter diodes. All the emitters distinguish themselves in offering high output power coupled into the plastic fiber. Data sheets for LEDs usually specify electrical and optical characteristics, out of which are important peak wavelength of emission, conversion efficiency (usually specified in terms of power launched in optical fiber for specified forward current), optical rise and fall times which put the limitation on operating frequency, maximum forward current through LED and typical forward voltage across LED.

Photo detectors usually come in variety of forms like photoconductive, photovoltaic, transistor type output and diode type output. Here also characteristics to be taken into account are response time of the detector, which puts the imitation on the operating frequency, wavelength sensitivity and responsivity.

## Procedure

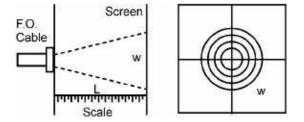

#### (A) Characteristics of Fiber Optic LED

- 1. Make the jumper and switch settings as shown in the jumper diagram. Keep pot P4 in fully clockwise position.

- 2. Connect the ammeter with the jumper connecting wires (provided along with the kit) in jumpers JP3 as shown in the diagram.

- 3. Connect the voltmeter with the jumper wires to JP5 and JP2 at positions as shown in the diagram.

- 4. Switch on the power supply. Keep the potentiometer P3 in its minimum position (fully anticlockwise position), P4 is used to control biasing voltage of the LED. To get the VI characteristics of LED, rotate P3 slowly and measure forward current and corresponding forward voltage of the LED, Take number of such readings for forward voltage, forward current & optical power. Keep SW towards VI position.

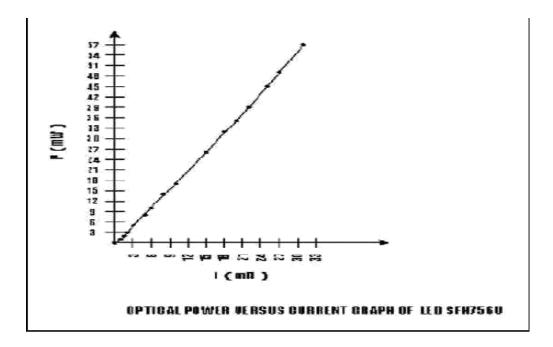

- 5. For each reading taken above, find out the power, which is product of I and V. This is the electrical power supplied to the LED. Data sheets for the LED specifies optical power coupled into plastic fiber when forward current was 10 micro A as 200microW. This means that the electrical power at 10mA current is converted into 200 micro W of optical energy. Hence the efficiency of the LED comes out to be approx. 1.15%.

- 6. With this efficiency assumed, find out optical power coupled into plastic optical fiber for each of the reading in step 4. Plot the graph of forward current v/s output optical power of the LED.

- 7. Repeat the above procedure by using SFH 450V (950 nm) LED.

#### 1) Characteristics of detector

Make the jumper and switch settings as shown in the jumper diagram. Keep pot P4 in fully clockwise position.

Connect the ammeter with the jumper connecting wires (provided along with the kit) in jumpers JP7 as shown in the diagram.

Connect 1Meter Fiber between TX1 & RX1.

Measure the current flowing through Detector (RX1) SFH250V at corresponding optical power output (Normally in u A) as per the table.

We can observe that as incident optical power on detector increases, current flowing through the detector increases.

## Observations

| Sl.No | Forward    | Forward    | Electrical | Optical power | Output current |

|-------|------------|------------|------------|---------------|----------------|

|       | Voltage of | Current of | Power      | of LED Po =   | (µ A)          |

|       | LED (V)    | LED (mA)   | Pi = V * I | Pi * 1.15%    |                |

|       |            |            |            |               |                |

|       |            |            |            |               |                |

#### **BLOCK DIAGRAM FOR CHARACTERISTICS OF LED & DETECTOR**

## Precautions

It is very important that the optical sources be properly aligned with the cable and the distance from the launched point and the cable be properly selected to ensure that the maximum amount of optical power is transferred to the cable.

## **Result:**

The characteristics of LED & DETECTOR are found